2.13 The individual memory cells used in computers are bistable in operation and capable of storing a single binary bit. Therefore, it is most practical to use the binary number system to represent numbers, and this system was explained along with conversion techniques to and from decimal.

Negative numbers are represented in computers by using a sign bit which is a 1 when the number is negative and a 0 for positive numbers. Negative numbers are often represented by using 1s or 2s complement form, and this was described along with examples showing how mixed numbers represented in that form can be added or subtracted.

The direct representation of decimal numbers can be accomplished by using a binary-coded-decimal (BCD) representation. This was explained, and examples were given.

The octal and hexidecimal number systems were described. These are useful in representing binary numbers in a compact form and to facilitate communication of values in written presentations. Computers are often organized with numbers represented in groups of 8 bits which makes hexadecimal particularly useful at this time.

# QUESTIONS

- 2.1 Convert the following decimal numbers to equivalent binary numbers:

- (a) 43

- (b) 64

- (c) 4096

- (d) 0.375

- (e)  $\frac{27}{32}$

- (f) 0.4375

- (g) 512.5

- (h) 131.5625

- (i) 2048.0625

- 2.2 Convert the following numbers to the equivalent binary numbers:

- (a) 14

- (b) 0.25

- (c)  $2\frac{1}{8}$

- (d) 6.25(e)  $2\frac{3}{8}$ (f) 0.625Convert the following binary numbers to equivalent decimal numbers: 2.3

- (a) 1101

- (b) 11011

- (c) 1011

- (d) 0.1011

- (e) 0.001101

- (f) 0.001101101

- (g) 111011.1011

- (h) 1011011.001101

- (i) 10110.0101011101

- Convert the following binary numbers to equivalent decimal numbers: 2.4

- (a) 1011

- (b) 11000

- (c) 100011

- (d) 11011

- (e) 111001

- (f) 1011010

- 2.5 Convert the following binary numbers to equivalent decimal numbers:

- (a) 1011

- (b) 100100

- (c) 10011

- (d) 0.1101

- (e) 0.1001

- (f) 0.0101

- (g) 1011.0011

- (h) 1001.1001

- (i) 101.011

- Convert the following binary numbers to equivalent decimal numbers: 2.6

- (a) 0.111

- (b) 0.11011

- (c) 1.011

- (d) 111.1011

- (e) 0110.0101

- (f) 101.101011

**NUMBER SYSTEMS**

| 2.7    | Perform the following additions and check by converting the binary numbers |

|--------|----------------------------------------------------------------------------|

| to dec | rimal:                                                                     |

(a) 1001.1 + 1011.01

(b) 100101 + 100101

(c) 0.1011 + 0.1101

(d) 1011.01 + 1001.11

**2.8** Perform the following additions and check by converting the binary numbers to decimal and adding:

(a) 1011 + 1110

(b) 1010 + 1111

(c) 10.11 + 10.011

(d) 1101.11 + 1.11

(e) 11111.1 + 10010.1

(f) 101.1 + 111.11

**2.9** Perform the following additions and check by converting the binary numbers to decimal:

(a) 1101.1 + 1011.1

(b) 101101 + 1101101

(c) 0.0011 + 0.1110

(d) 1100.011 + 1011.011

**2.10** Perform the following subtractions in binary and check by converting the numbers to decimal and subtracting:

(a) 1101 - 1000

(b) 1101 - 1001

(c) 1011.1 - 101.1

(d) 1101.01 - 1011.1

(e) 111.11 - 101.1

(f) 1101.1 - 1010.01

2.11 Perform the following subtractions in the binary number system:

(a) 64 - 32

(b) 127 - 63

(c) 93.5 - 42.75

(d)  $84\frac{9}{32} - 48\frac{5}{16}$

**2.12** Perform the following subtractions in the binary number system:

(a) 128 - 32

(b)  $\frac{1}{8} - \frac{1}{16}$

$(c) \ 2\frac{1}{8} - 4\frac{3}{32}$

(d)  $31 - \frac{5}{8}$

(e)  $62 - 31\frac{1}{16}$

(f) 129 - 35

2.13 Perform the following subtractions in the binary number system:

(a) 37 - 35

(b) 128 - 64

(c) 94.5 - 43.75

(d) 255 - 127

**2.14** Perform the following multiplications and divisions in the binary number system:

(a)  $16 \times 8$

(b)  $31 \times 14$

(c)  $23 \times 3.525$

(d)  $15 \times 8.625$

(e)  $6 \div 2$

$(f) 16 \div 8$

2.15 Perform the following multiplications and divisions in the binary number system:

(a)  $24 \times 12$

(b)  $18 \times 14$

(c)  $32 \div 8$

(a)  $24 \times 12$ (d)  $27 \div 18$

(e) 49.5 × 51.75

(f) 58.75 ÷ 23.5

**2.16** Perform the following multiplications and divisions in the binary number system:

(a)  $16 \times 2.75$

(b)  $19 \div 6$

(c)  $256\frac{1}{2} \div 128\frac{1}{4}$

(d) 31.5 ÷ 15.75

(e)  $3 \div \frac{5}{8}$

$(f) 2\frac{5}{8} \times 1\frac{5}{8}$

**2.17** Perform the following multiplications and divisions in the binary number system:

(a)  $15 \times 13$

(b)  $10 \times 15$

(c) 44 ÷ 11

$(d) 42 \div 12$

(e)  $7.75 \times 2.5$

(f) 22.5  $\times$  4.75

QUESTIONS

| <b>2.18</b> ments: |                                     | following d                    | lecimal num                             | pers to both the                          | ir 9s and 10s comple-                                    |

|--------------------|-------------------------------------|--------------------------------|-----------------------------------------|-------------------------------------------|----------------------------------------------------------|

|                    | (a) 9<br>(d) 24                     | (b) 19<br>(e) 25               | (c)<br>(f)                              | 8<br>99                                   |                                                          |

| <b>2.19</b> ments: | Convert the                         | following d                    | ecimal numb                             | ers into both the                         | eir 9s and 10s comple-                                   |

|                    | (a) 5436                            | (b) 1                          | 932                                     | (c) 45.15                                 | (d) 18.293                                               |

| <b>2.20</b> ments: | Convert the                         | following d                    | ecimal numb                             | ers into both the                         | eir 9s and 10s comple-                                   |

|                    | (a) 95<br>(d) 0.16                  | (b) 7 (e) 2                    | 9<br>98.64                              | (c) 0.83<br>(f) 332.52                    |                                                          |

| <b>2.21</b> ments: |                                     |                                |                                         |                                           | ir 9s and 10s comple-                                    |

|                    | (a) 3654                            | (b) 2                          | 122                                     | (c) 54.19                                 | (d) 37.263                                               |

| 2.22               | Convert the (a) 1101 (d) 1110       | following bi<br>(b) 1<br>(e) 1 | 010                                     | s to both their 1<br>(c) 1111<br>(f) 1011 | s and 2s complements:                                    |

| 2.23               | Convert the (a) 1011                | following bi<br>(b) 1          |                                         | s to both their 1<br>(c) 1011.01          | s and 2s complements:<br>(d) 11011.01                    |

| 2.24               | Convert the (a) 1011 (d) 0.101      | (b)                            | nary number<br>1101<br>11.101           | (c) 0.0111<br>(f) 101.011                 | s and 2s complements:                                    |

| 2.25               | Convert the (a) 101111 (c) 10111.1  | (1                             | nary number<br>b) 100100<br>d) 10011.11 | s to both their 1                         | s and 2s complements:                                    |

| 2.26               | Perform the (a) 8 - 4 (d) 28.5 -    |                                | (b) 16 –<br>(e) 27.6                    | 8                                         | nd 10s complements:<br>(c) 198 - 124<br>(f) 0.55 - 0.42  |

| 2.27               | Perform the (a) 948 - 2 (c) 349.5 - | 234                            | (b) 347                                 | using both 9s and 1 - 263<br>2.7 - 409.2  | nd 10s complements:                                      |

|                    |                                     | _                              | (b) $15 -$                              | 9 .                                       | nd 10s complements:<br>(c) 0.5 - 40.24<br>(f) 1.2 - 0.34 |

| 2.29               | Perform the (a) 1024 - (c) 24.1 -   | 913                            | (b) 249 -<br>(d) 239.3                  | 137                                       | nd 10s complements:                                      |

|                    | Perform the plements:               | following s                    | subtractions of                         | of binary numb                            | ers, using both 1s and                                   |

|                    | (a) 1010 -                          |                                | (b) 110 -<br>(e) 0.111                  |                                           | (c) 110 - 0.111<br>(f) 11.11 - 10.111                    |

|                    |                                     |                                |                                         |                                           |                                                          |

**NUMBER SYSTEMS**

- **2.31** Perform the following subtractions, using both 1s and 2s complements:

- (a) 1011 101

- (b) 11011 11001

- (c) 10111.1 10011.1

- (d) 11011 10011.11

- **2.32** How many different numbers can be stored in a set of four switches, each having three different positions (four three-position switches)?

- **2.33** How many different binary numbers can be stored in a register consisting of six switches?

- **2.34** How many different BCD numbers can be stored in 12 switches? (Assume two-position, or on-off switches.)

- **2.35** How many different BCD numbers can be stored in a register containing 12 switches using an 8, 4, 2, 1 code? Using an excess-3 code?

- **2.36** Write the first 12 numbers in the base 4 (or quaternary) number system.

- **2.37** Write the first 10 numbers in the quaternary number system, which has a base, or radix, of 4. Use the digits 0. 1, 2, and 3 to express these numbers.

- **2.38** Write the first 20 numbers in the base 12 (or *duodecimal*) number system. Use A for 10 and B for 11.

- **2.39** Write the first 25 numbers in a base 11 number system, using the digits 0, 1, 2, 3, 4, 5, 6, 7, 8; 9, and A to express the 25 numbers that you write. (Decimal 10 = A, for instance.)

- **2.40** Perform the following subtractions in the binary number system, using 1s complements:

- (a) 1111 1001

- (b) 1110 1011

- (c) 101.11 101.01

- (d) 111.1 100.1

- **2.41** Using the 1s complement number system, perform the following subtractions:

- (a) 0.1001 0.0110

- (b) 0.1110 0.0110

- (c) 0.01111 0.01001

- (d) 11011 11001

- (e) 1110101 1010010

- **2.42** Perform the following subtractions in the binary number system, using 2s complements:

- (a) 1111 110

- (b) 1110 1100

- (c) 1011.11 101.001

- (d) 111.1 110.1

- **2.43** Using the 2s complement number system, perform the following subtractions and represent the answers as decimal fractions:

- (a) 0.101010 0.010101

- (b) 0.11001 0.00100

- (c) 0.111000 0.000111

- (d) 0.101100 0.010011

- **2.44** Convert the following hexadecimal numbers to decimal numbers:

- (a) 15

- (b) B8

- (c) AB4

- (d) 9.B

- (e) 9.1A

- **2.45** Convert the following hexadecimal numbers to decimal:

- (a) B6C7

- (b) 64AC

- (c) A492

- (d) D2763

| 2.46 | Convert the followard (a) 15 (d) 124              | owing octal number (b) 125 (e) 156           | ers to decimal:<br>(c) 115<br>(f) 15.6 |                                    |            | 55            |

|------|---------------------------------------------------|----------------------------------------------|----------------------------------------|------------------------------------|------------|---------------|

| 2.47 | Convert the followard (a) 2376                    | owing octal number (b) 2473                  | ers to decimal:<br>(c) 276431          |                                    | 22632      |               |

| 2.48 | Convert the follo<br>(a) 110<br>(d) 0.11111       | (b) 111001<br>(e) 10.11                      | (c) 1                                  | 11.111<br>111.1101                 |            |               |

| 2.49 | Convert the follo<br>(a) 101101<br>(d) 110110.011 | (b) 1011<br>(e) 011.1                        | 01110                                  | (c) 101101                         | 111        | QUESTIONS     |

| 2.50 | Convert the follo (a) 54 (d) 232.4                | wing octal numbe<br>(b) 44<br>(e) 453.45     | rs to binary:<br>(c) 232<br>(f) 31.2   |                                    | SRINIVAS ( | COLLEGE OF    |

| 2.51 | Convert the followard (a) 7423 (d) 3232.14        | wing octal numbe<br>(b) 3364<br>(e) 3146.52  | •                                      | (c) 33762                          | ACC No.:   | SELON STUDIES |

| 2.52 | Convert the followard (a) 17 (d) 0.55             | wing decimal num (b) 8 (e) 0.625             | (c) 19<br>(f) 2.125                    | ·                                  |            |               |

| 2.53 | Convert the followard (a) 932 (d) 632.97          | wing decimal num<br>(b) 332<br>(e) 4429.625  |                                        | 45.375                             |            |               |

| 2.54 | Convert the followard (a) 9 (d) 0.AB              | wing hexadecimal (b) 1B (e) AB               | numbers to bi<br>(c) 0.A1<br>(f) 12.B  | inary:                             |            |               |

| 2.55 | Convert the followard (a) CD (d) AA.1A            | wing hexadecimal<br>(b) 6A9<br>(e) AB2.234   | numbers to bi                          | •                                  |            |               |

| 2.56 | Convert the followard (a) 1101.0110 (d) 11101     | wing binary numb<br>(b) 110111<br>(e) 11110. | 110                                    | eimal:<br>(c) 1111<br>(f) 1011.110 | 010        |               |

| 2.57 | Convert the followard (a) 10110111 (d) 0.01111110 | wing binary numb<br>(b) 1001<br>(e) 10110    | 1100                                   | imal:<br>(c) 10011                 | 111        |               |

**2.58** A simple rule for multiplying two digits in any radix is simply to multiply the two digits in decimal. If the product is less than the radix, take it; if greater, divide (in decimal) by the radix and use the remainder as the first, or least significant, position and the quotient as the carry, or most significant, digit. In base 6, then  $2 \times 2 = 4$ ,  $3 \times 1 = 3$ , etc.; however,  $2 \times 4 = 8$ , and

Then regrouping yields

So

$412_{10} = 19C$

NUMBER SYSTEMS

Convert the following decimal numbers to hexadecimal:

(a) 24

(b) 397

(c) 1343

(d) 513

(e) 262

# BOOLEAN ALGEBRA AND GATE NETWOOKS

Modern digital computers are designed and maintained, and their operation is analyzed, by using techniques and symbology from a field of mathematics called *modern algebra*. Algebraists have studied for over a hundred years mathematical systems called *boolean algebras*. Nothing could be more simple and normal to human reasoning than the rules of boolean algebra, for these originated in studies of how we reason, what lines of reasoning are valid, what constitutes proof, and other allied subjects.

The name boolean algebra honors a fascinating<sup>1</sup> English mathematician, George Boole, who in 1854 published a classic book, An Investigation of the Laws of Thought, on Which Are Founded the Mathematical Theories of Logic and Probabilities. Boole's stated intention was to perform a mathematical analysis of logic.

Starting with his investigation of the laws of thought, Boole constructed a "logical algebra." This investigation into the nature of logic and ultimately of mathematics led subsequent mathematicians and logicians into several new fields of mathematics. Two of these, known as the *calculus of propositions* and the *algebra of sets*, were based principally on Boole's work. In this book we designate the algebra now used in the design and maintenance of logical circuitry as *boolean algebra*.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>George Boole was the son of a shoemaker. His formal education ended in the third grade. Despite this, he was a brilliant scholar, teaching Greek and Latin in his own school, and an accepted mathematician who made lasting contributions in the areas of differential and difference equations as well as in algebra.

<sup>&</sup>lt;sup>2</sup>This algebra is sometimes called *switching algebra*. It is, in fact, only one of several realizations of what modern algebraists call boolean algebra.

BOOLEAN ALGEBRA AND GATE NETWORKS

There are several advantages in having a mathematical technique for the description of the internal workings of a computer. For one thing, it is often far more convenient to calculate with expressions used to represent switching circuits than it is to use schematic or even logical diagrams. Further, just as an ordinary algebraic expression may be simplified by means of the basic theorems, the expression describing a given switching circuit network may be reduced or simplified. This enables the logical designer to simplify the circuitry used, achieving economy of construction and reliability of operation. Boolean algebra also provides an economical and straightforward way of describing the circuitry used in computers. In all, a knowledge of boolean algebra is indispensable in the computing field.

### **OBJECTIVES**

- 1 The design and maintenance of digital computers are greatly facilitated by the use of boolean algebra and block diagrams. Both of these are explained, as is their usage in designing networks using logic gates.

- 2 The major types of gates now in use are AND, OR, NOR, and NAND gates. These are explained, and design procedures using these gates are presented.

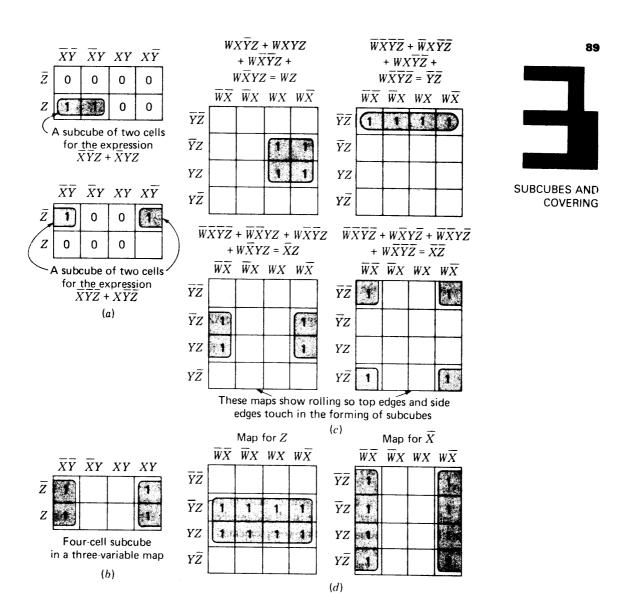

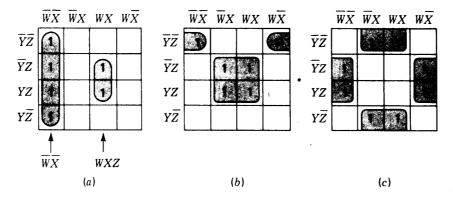

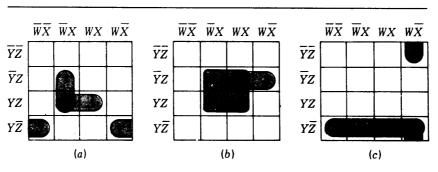

- 3 To simplify the construction of computers, the gate networks are simplified as much as possible. Both algebraic techniques and graphical (map) techniques exist which can be used; both are discussed with emphasis on the map minimization procedures.

- 4 Logic networks are generally laid out in a two-level form such as AND-OR, NAND-NAND, etc. These forms are described, and design procedures for the forms are presented.

- 5 There are several special characteristics of gates which can influence logic design (such as wired OR and wired AND gates). These are described, as are special forms such as NAND-AND and NOR-OR.

- 6 Integrated-circuit (IC) manufacturing techniques now make it possible to package many gates in a single IC package (chip). Often these arrays of gates are laid out in some regular form for large-scale integration and typical forms are presented, including those for programmable logic arrays, programmable array logic, and gate array logic.

# **FUNDAMENTAL CONCEPTS OF BOOLEAN ALGEBRA**

**3.1** When a variable is used in an algebraic formula, it is generally assumed that the variable may take any numerical value. For instance, in the formula 2X - 5Y = Z, we assume that X, Y, and Z may range through the entire field of real numbers.

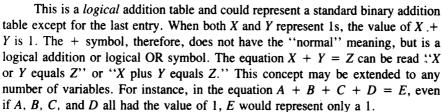

The variables used in boolean equations have a unique characteristic, however; they may assume only one of two possible values. These two values may be represented by the symbols 0 and 1.† If an equation describing logical circuitry has several variables, it is still understood that each of the variables can assume only the value 0 or 1. For instance, in the equation X + Y = Z, each of the variables X, Y, and Z may have only the values 0 or 1.

This concept will become clearer if a symbol is defined, the + symbol. When the + symbol is placed between two variables, say X and Y, since both X and Y can take only the role 0 or 1, we can define the + symbol by listing all possible combinations for X and Y and the resulting values of X.

The possible input and output combinations may be arranged as follows:

$$0 + 0 = 0$$

$0 + 1 = 1$

$1 + 0 = 1$

$1 + 1 = 1$

To avoid ambiguity, a number of other symbols have been recommended as replacements for the + sign. Some of these<sup>3</sup> are  $\cup$ ,  $\mathbf{v}$ , and  $\mathbf{V}$ . Computer people still use the + sign, however, which was the symbol originally proposed by Boole,

# **LOGICAL MULTIPLICATION**

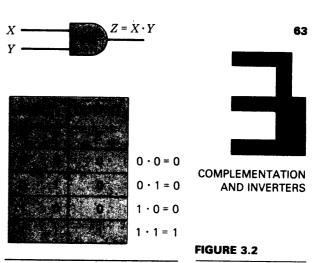

**3.2** A second important operation in boolean algebra we call *logical multiplication* or the *logical* AND *operation*.<sup>4</sup> The rules for this operation can be given by simply listing all values that might occur:

$$0.0 = 0$$

$0.1 = 0$

$1.0 = 0$

$1.1 = 1$

Thus, for instance, if we write  $Z = X \cdot Y$  and find X = 0 and Y = 1, then Z = 0. Only when X and Y are both 1s would Z be a 1.

Both + and  $\cdot$  obey a mathematical rule called the *associative law*. This law says, for +, that (X + Y) + Z = X + (Y + Z) and, for  $\cdot$ , that  $X \cdot (Y \cdot Z) = (X \cdot Y) \cdot Z$ . This means that we can write X + Y + Z without ambiguity, for no matter in what order the operation is performed, the result is the same. That is,

<sup>&</sup>lt;sup>3</sup>The preceding equation might then be written  $A \cup B \cup C \cup D = E$ .

<sup>&</sup>lt;sup>4</sup>It is necessary to know both the terms logical addition and OR operation for the + symbol and the terms logical multiplication and AND operation for the · symbol since all these terms are actively used in computer manuals, technical journals, and trade magazines. The term X + Y is called a *sum term* or OR term in computer literature, for example.

BOOLEAN ALGEBRA AND GATE NETWORKS

ORing X and Y and then ORing Z gives the same result as ORing Y and Z and then ORing X. We can test this for both + and  $\cdot$  by trying all combinations.

Note that while either +'s or 's can be used freely, the two cannot be mixed without ambiguity in the absence of further rules. For instance, does  $A \cdot B + C$  mean  $(A \cdot B) + C$  or  $A \cdot (B + C)$ ? The two form different values for A = 0, B = 0, and C = 1, for then we have  $(0 \cdot 0) + 1 = 1$  and  $0 \cdot (0 + 1) = 0$ , which differ. (Always operating from left to right will alleviate this. This technique is used in some programming languages, but not usually by algebraists or computer designers or maintenance personnel.) The rule which is used is that  $\cdot$  is always performed before +. Thus  $X \cdot Y + Z$  is the same as  $(X \cdot Y) + Z$ , and  $X \cdot Y + X \cdot Z$  means the same as  $(X \cdot Y) + (X \cdot Z)$ .

# **AND GATES AND OR GATES**

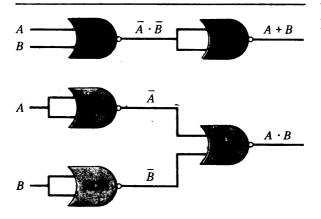

**3.3** The + and · operations are physically realized by two types of electronic circuits, called *OR gates* and *AND gates*. We treat these as "black boxes," deferring until later any discussion of how the actual circuitry operates.

A gate is simply an electronic circuit which operates on one or more input signals to produce an output signal. One of the simplest and most frequently used gates is called the OR gate, and the block diagram symbol for the OR gate is shown in Fig. 3.1, as is the table of combinations for the inputs and outputs for the OR gate. Since the inputs X and Y are signals with values either 0 or 1 at any given time, the output signal Z can be described by simply listing all values for X and Y and the resulting value for Z. A study of the table in Fig. 3.1 indicates that the OR gate ORs or logically adds its inputs.

Similarly, the AND gate in Fig. 3.2 ANDs or logically multiplies input values, yielding an output Z with value  $X \cdot Y$ , so that Z is a 1 only when both X and Y are 1s.

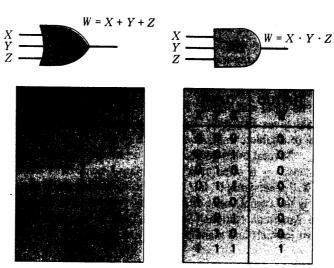

Just as the + and  $\cdot$  operations could be extended to several variables by using the associative law, OR gates and AND gates can have more than two inputs. Figure 3.3 shows three input OR and AND gates and the table of all input combinations for each. As might be hoped, the OR gate with input X, Y, and Z has a 1 output if X or Y or Z is a 1, so that we can write X + Y + Z for its output.

FIGURE 3.1

OR gate.

FIGURE 3.3

AND gate.

Three-input OR and AND gates.

Also, the output of the AND gate with inputs, X, Y, and Z is a 1 only when all three of the inputs are 1s, so that we can write the output as  $X \cdot Y \cdot Z$ .

The above argument can be extended. A four-input OR gate has a 1 output when any of its inputs is a 1, and a four-input AND gate has a 1 output only when all four inputs are 1s.

It is often convenient to shorten  $X \cdot Y \cdot Z$  to XYZ, and we sometimes use this convention.

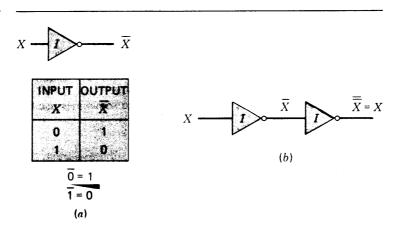

# **COMPLEMENTATION AND INVERTERS**

**3.4** The two operations defined so far have been what algebraists would call binary operations in that they define an operation on two variables. There are also singular or unary, operations, which define an operation on a single variable. A

64

BOOLEAN ALGEBRA AND GATE NETWORKS

familiar example of unary operation is -, for we can write -5 or -10 or -X, meaning that we are to take the negative of these values. (The - is also used as a binary operation symbol for subtraction, which makes it a familiar but ambiguous example.)

In boolean algebra we have an operation called *complementation*, and the symbol we use is  $\overline{X}$ . Thus we write  $\overline{X}$ , meaning "take the complement of X," or  $\overline{X}$ , meaning "take the complement of X + Y." The complement operation can be defined quite simply:

$$\frac{\overline{0}}{\overline{1}} = 1$$

The complement of a value can be taken repeatedly. For instance, we can find  $\overline{X}$ : For X = 0 it is  $\overline{0} = \overline{1} = \overline{0} = 1$ , and for X = 1 it is  $\overline{1} = \overline{0} = \overline{1} = 0$ .

A useful rule is based on the fact that  $\overline{X} = X$ . Checking, we find that  $\overline{0} = \overline{1} = 0$  and  $\overline{1} = \overline{0} = 1$ . [This rule—that double complementation gives the original value—is an important characteristic of a boolean algebra which does not generally hold for most unary operations. For instance, the rule does not hold for the operation of squaring a real number:  $(3^2)^2 = 81$ , not 3.]

The complementation operation is physically realized by a gate or circuit called an *inverter*. Figure 3.4(a) shows an inverter and the table of combinations for its input and output. Figure 3.4(b) shows also that connecting two inverters in series gives an output equal to the input, and this is the gating counterpart to the law of double complementation,  $\overline{X} = X$ .

Several other symbols have been used for the complementation symbol. For instance,  $\sim$  is often used by logicians who write  $\sim X$  and read this "the negation of X." The symbol 'has been used by mathematicians and computer people; thus X' is the complement of X in these systems. The overbar symbol is now used by the American National Standards Institute and military standards, as well as by most journals and manufacturers, and we use it.

### FIGURE 3.4

(a) Block diagram of an inverter. (b) Two inverters in series.

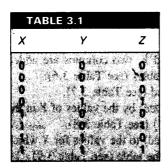

**3.5** The tables of values for the three operations just explained are sometimes called *truth tables*, or *tables of combinations*. To study a logical expression, it is very useful to construct a table of values for the variables and then to evaluate the expression for each of the possible combinations of variables in turn. Consider the expression  $X + Y\overline{Z}$ . There are three variables in this expression: X, Y, and Z, each of which can assume the value 0 or 1. The possible combinations of values may be arranged in ascending order,  $^5$  as in Table 3.1.

One of the variables, Z, is complemented in the expression  $X + Y\overline{Z}$ . So a column is now added to the table listing values of  $\overline{Z}$  (see Table 3.2).

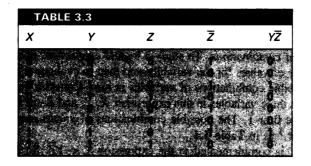

A column is now added listing the values that  $Y\overline{Z}$  assumes for each value of X, Y, and Z. This column will contain the value 1 only when both Y is a 1 and  $\overline{Z}$  is a 1 (see Table 3.3).

Now the ORing, or logical addition, of the values of X to the values which have been calculated for  $Y\overline{Z}$  is performed in a final column (see Table 3.4).

The final column contains the value of  $X + Y\overline{Z}$  for each set of input values which X, Y, and Z may take. For instance, when X = 1, Y = 0, and Z = 1, the expression has the value of 1.

<sup>&</sup>lt;sup>5</sup>Note that the variables in each row of this table may be combined into a binary number. The binary numbers will then count from 000 to 111 in binary, or from 0 to 7 decimal. Sometimes each row is numbered in decimal according to the number represented. Then reference may be made to the row by using the decimal number. For instance, row 0 has values of 0, 0, 0, for X, Y, and Z, row 6 has values of 1, 1, 0, and row 7 has values of 1, 1, 1.

| TAB | LE 3.2 |     |     |  |

|-----|--------|-----|-----|--|

| X   | Y      | Z   | Z   |  |

| ۵   | '0     | n   | •   |  |

| ō   | ō      | . j | ò   |  |

| 0   | 1      | 0   | 1   |  |

| 1   | 0      | 0.4 | - 4 |  |

|     | . 1    |     | . 1 |  |

| 1   | *1     | . 1 | . 0 |  |

EVALUATION OF LOGICAL EXPRESSIONS

BOOLEAN ALGEBRA AND GATE NETWORKS

| TAB | LE 3.4           |               |                     |                        |                      |

|-----|------------------|---------------|---------------------|------------------------|----------------------|

| X   | Y                | Z             | Z                   | ΥZ̈                    | $X + Y\overline{Z}$  |

|     | Sustant at       | X LOUIS       | with in             | file dispus            | o Ocasida            |

| 4   | e s <b>e</b> lla | at an late.   | <b>bati P</b> ai ti | апофе, г               | in of femilia.       |

|     |                  | ary Principal | 10-                 | unin <b>h</b> e val    | tras <b>o</b> radios |

|     |                  |               | 4 1277              | neten <b>o</b> ro<br>O | Art Art . in         |

|     | 1                |               | Ī                   | 1                      | **                   |

|     |                  |               | . 0                 | 0                      | 1                    |

# **EVALUATION OF AN EXPRESSION CONTAINING PARENTHESES**

**3.6** The following example illustrates the procedure for constructing a truth table for the expression  $X + Y(\overline{X} + \overline{Y})$ . There are only two variables in the expression, X and Y. First a table of the values which X and Y may assume is constructed (see Table 3.5).

Now, since the expression contains both  $\overline{X}$  and  $\overline{Y}$ , two columns are added listing complements of the original values of the variables (see Table 3.6).

The various values of  $\overline{X} + \overline{Y}$  are now calculated (see Table 3.7).

The values for  $\overline{X} + \overline{Y}$  are now multiplied (ANDed) by the values of Y in the table, forming another column representing  $Y(\overline{X} + \overline{Y})$  (see Table 3.8).

Finally the values for  $Y(\overline{X} + \overline{Y})$  are added (ORed) to the values for X which are listed, forming the final column and completing the table (see Table 3.9).

Inspection of the final column of the table indicates that the values taken by the function  $X + Y(\overline{X} + \overline{Y})$  are identical with the values found in the table for ORing X and Y. This indicates that the function  $X + Y(\overline{X} + \overline{Y})$  is equivalent to

| TAB | LE 3.6      |                  |                  |

|-----|-------------|------------------|------------------|

| X   | Y           | X                | 7                |

| 0   | 0<br>1<br>0 | 1<br>1<br>0<br>0 | 1<br>0<br>1<br>0 |

| TABI | LE 3.7 |                |                |                               |

|------|--------|----------------|----------------|-------------------------------|

| X    | Υ      | $\overline{X}$ | $\overline{Y}$ | $\overline{X} + \overline{Y}$ |

| 0    | 0      |                | 1              |                               |

| 0    | 1      | ě,             | 0              | 1                             |

| 1    | 0      | 0 '            | 1              | 1                             |

| BAS<br>BOOLEA | WS OF<br>GEBRA |

|---------------|----------------|

| TAB    | LE 3.8 |                 |                |                                                                                                                |                                  |

|--------|--------|-----------------|----------------|----------------------------------------------------------------------------------------------------------------|----------------------------------|

| X      | Y      | $\overline{X}$  | $\overline{Y}$ | $\overline{X} + \overline{Y}$                                                                                  | $Y(\overline{X} + \overline{Y})$ |

| 0 57.5 | σ      | Service and the | 1 1 1 1 1 1 1  | and the state of the                                                                                           |                                  |

| 0      | 1      | 1               | 0              | entra de la companya | 1 3 3 3                          |

| i      |        | 0 .             | o.             | 4                                                                                                              |                                  |

| TAE  | BLE 3.9                               | LE 3.9         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |                                  |                                      |

|------|---------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------|--------------------------------------|

| X    | Y                                     | $\overline{x}$ | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\overline{X} + \overline{Y}$ | $Y(\overline{X} + \overline{Y})$ | $X + Y(\overline{X} + \overline{Y})$ |

| ^    | Λ                                     |                | . Personal de la companya de la com |                               |                                  |                                      |

| 0    | ĭ                                     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ti i kaaki sin                | 4                                | (Terminal)                           |

| * // | ó                                     | ò              | 7 -1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U. P. B. BOOM                 |                                  | P S ROLL SEE                         |

| 4    | * * * * * * * * * * * * * * * * * * * | A              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A                             | A                                | 1.40 + 2.                            |

the function X + Y. This equivalence has been established by trying each possible combination of values in the variables and noting that both expressions then have the same value. This is called a *proof by perfect induction*. If a logic circuit were constructed for each of the two expressions, both circuits would perform the same function, yielding identical outputs for each combination of inputs.

# **BASIC LAWS OF BOOLEAN ALGEBRA**

**3.7** Some fundamental relations of boolean algebra have been presented. A complete set of the basic operations is listed below. Although simple in appearance,

<sup>&</sup>lt;sup>6</sup>Actually, a number of possible sets of postulates may be used to define the algebra. The particular treatment of boolean algebra given here is derived from that of E. V. Huntington and M. H. Stone. The author would also like to acknowledge the influence of I. S. Reed and S. H. Caldwell on this development of the concepts of the algebra.

BOOLEAN ALGEBRA AND GATE NETWORKS

```

TABLE 3.10 BOOLEAN ALGEBRA RULES

1 0 + X = X

2 1 + X = 1

3 X + X = X

4 X + X = 1

5 0 · X = 0

6 1 · X = X

7 X \cdot X = X

8 X \cdot X = 0

9 X = X

10 X + Y = Y + X

11 X \cdot Y = Y \cdot X

12 X + (Y + Z) = (X + Y) + Z

13 X(YZ) = (XY)Z

14 X(Y + Z) = XY + XZ

15 X + XZ = X

16 X + XZ = X

17 (X + Y)(X + Z) = X + YZ

18 X + XY = X + Y

19 XY + YZ + YZ = XY + Z

```

these rules may be used to construct a boolean algebra, determining all the relations that follow:

If

$$X \neq 0$$

, then  $X = 1$

and

If

$$X \neq 1$$

, then  $X = 0$

| OR OPERATION (LOGICAL ADDITION) | AND OPERATION (LOGICAL MULTIPLICATION) | COMPLEMENT RULES   |

|---------------------------------|----------------------------------------|--------------------|

| 0 + 0 = 0                       | 0.0 = 0                                | $\overline{0} = 1$ |

| 0 + 1 = 1                       | 0.0 = 0                                | $\overline{1} = 0$ |

| 1 + 0 = 1                       | $1 \cdot 0 = 0$                        |                    |

| 1 + 1 = 1                       | $1 \cdot 1 = 1$                        |                    |

A list of useful relations is presented in Table 3.10. Most of the basic rules by which boolean algebra expressions may be manipulated are contained in this table. Each rule may be proved by using the proof by perfect induction. An example of this proof for rule 3 in Table 3.10 is as follows: The variable X can have only the value 0 or 1. If X has the value 0, then 0 + 0 = 0; if X has the value 1, then 1 + 1 = 1. Therefore X + X = X.

These rules are used to construct an *example*, or *realization*, of a boolean algebra. We note that, strictly speaking, this boolean algebra consists of a set B of two elements which we call 0 and 1, an addition operation +, a multiplication operation ·, and a complement operation ·. There are other boolean algebras (an infinite number), but this was Boole's original algebra. This algebra is sometimes called *switching algebra* to identify it more closely, but it is the same as propositional calculus, for instance.

The same basic technique may be used to prove the remainder of the rules. Rule 9 states that double complementation of a variable results in the original variable. If X equals 0, then the first complement is 1 and the second will be 0, the original value. If the original value for X is 1, then the first complement will be 0 and the second 1, the original value. Therefore  $X = \overline{X}$ .

Rules 10 and 11, which are known as the *commutative laws*, express the fact that the order in which a combination of terms is performed does not affect the result of the combination. Rule 10 is the commutative law of addition, which states that the order of addition or ORing does not affect the sum (X + Y = Y + X). Rule 11 is the commutative law of multiplication (XY = YX), which states that the order of multiplication or ANDing does not affect the product.

Rules 12 and 13 are the associative laws. Rule 12 states that in the logical addition of several terms, the sum which will be obtained if the first term is added to the second and then the third term is added will be the same as the sum obtained if the second term is added to the third and then the first term is added [X + (Y + Z) = (X + Y) + Z]. Rule 13 is the associative law of logical multiplication, stating that in a product with three factors, any two may be multiplied, followed by the third [X(YZ) = (XY)Z].

Rule 14, the *distributive law*, states that the product of a variable (X) times a sum (Y + Z) is equal to the sum of the products of the variable multiplied by each term of the sum [X(Y + Z) = XY + XZ].

The three laws, commutative, associative, and distributive, may be extended to include any number of terms. For instance, the commutative law for logical addition states that X + Y = Y + X. This may be extended to

$$X + Y + Z + A = A + Y + Z + X$$

The commutative law for logical multiplication also may be extended: XYZ = YZX. These two laws are useful in rearranging the terms of an equation.

The terms also may be combined:

$$(X + Y) + (Z + A) = (A + Y) + (X + Z)$$

and (XY)(ZA) = (XA)(ZY). These two laws are useful in regrouping the terms of an equation.

The distributive law may be extended in several ways:

$$X(Y + Z + A) = XY + XZ + XA$$

If two sums, such as W + X and Y + Z, are to be multiplied, then one of the sums is treated as a single term and multiplied by the individual terms of the other sum. The results are then multiplied according to the distributive law. For instance.

$$(W + X)(Y + Z) = W(Y + Z) + X(Y + Z) = WY + WZ + XY + XZ$$

BASIC LAWS OF BOOLEAN ALGEBRA

BOOLEAN ALGEBRA AND GATE NETWORKS

# **PROOF BY PERFECT INDUCTION**

**3.8** Notice that, among others, rule 17 does not apply to "normal" algebra. The rule may be obtained from the preceding rules as follows:

$$(X + Y)(X + Z) = XX + XZ + XY + YZ$$

where  $XX = X$ , rule 7

$= X + XZ + XY + YZ$

$= X + XY + XZ + YZ$

$= X(1 + Y) + Z(X + Y)$  where  $1 + Y = 1$ , rule 2

$= X + Z(X + Y)$

$= X + XZ + YZ$

$= X(1 + Z) + YZ$  where  $1 + Z = 1$ , rule 2

$= X + YZ$

Therefore

$$(X + Y)(X + Z) = X + YZ$$

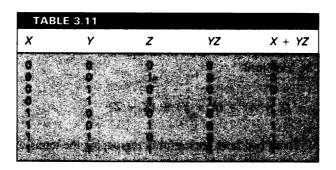

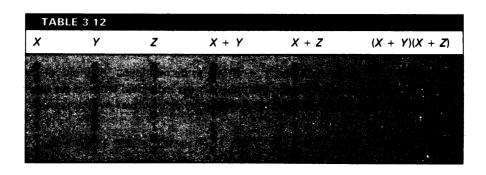

Since rule 17 does not apply to normal algebra, it is interesting to test the rule by using the proof by perfect induction. It will be necessary to construct truth tables for the right-hand (X + YZ) and left-hand [(X + Y)(X + Z)] members of the equation and compare the results (see Tables 3.11 and 3.12).

The last column of the table for the function X + YZ is identical with the last column of the table for (X + Y)(X + Z). This proves (by means of the proof by perfect induction) that the expressions are equivalent.

Rules 15 and 16 are also not rules in normal algebra. The following is a

$$X + XZ = X(1 + Z)$$

distributive law

And since 1 + Z = 1 by rule 2,

$$X + XZ = X(1)$$

and  $X(1) = X$  by rule 6

Therefore

$$X + XZ = X$$

It is worthwhile to try to prove rule 15 by using the proof by perfect induction at this point. Here is a proof of rule 16 that uses rules that precede it:

$$X(X + Y) = XX + XY$$

distributive law

$= X + XY$  (since  $XX = X$ )

$= X(1 + Y)$  where  $1 + Y = 1$ , rule 2

$= X$

It is instructive to prove this rule also by perfect induction at this point.

# SIMPLIFICATION OF EXPRESSIONS

**3.9** The rules given may be used to simplify boolean expressions, just as the rules of normal algebra may be used to simplify expressions. Consider the expression

$$(X + Y)(X + \overline{Y})(\overline{X} + Z)$$

The first two terms consist of X + Y and  $X + \overline{Y}$ ; these terms may be multiplied and, since  $X + X\overline{Y} + XY = X$  and  $Y\overline{Y} = 0$ , reduced to X.

The expression has been reduced now to  $X(\overline{X} + Z)$ , which may be expressed as  $X\overline{X} + XZ$  (rule 14). And since  $X\overline{X}$  is equal to 0, the entire expression  $(X + Y)(X + \overline{Y})(\overline{X} + Z)$  may be reduced to XZ.

Another expression that may be simplified is  $XYZ + X\overline{Y}Z + XY\overline{Z}$ . First the three terms  $XYZ + X\overline{Y}Z + XY\overline{Z}$  may be written  $X(YZ + \overline{Y}Z + Y\overline{Z})$ , by rule 14. Then, by using rule 14 again,  $X[Y(Z + \overline{Z}) + \overline{Y}Z]$ ; and since  $Z + \overline{Z}$  equals 1, we have  $X(Y + \overline{Y}Z)$ .

The expression  $X(Y + \overline{Y}Z)$  may be further reduced to X(Y + Z) by using rule 18. The final expression can be written in two ways: X(Y + Z) or XY + XZ. The first expression is generally preferable if the equation is to be constructed as an electronic circuit, because it requires only one AND circuit and one OR circuit.

# **DE MORGAN'S THEOREMS**

**3.10** The following two rules are known as De Morgan's theorems:

$$(\overline{X + Y}) = \overline{X} \cdot \overline{Y}$$

$$(\overline{X \cdot Y}) = \overline{X} + \overline{Y}$$

**BOOLEAN ALGEBRA** AND GATE **NETWORKS**

The complement of any boolean expression, or a part of any expression, may be found by means of these theorems. In these rules, two steps are used to form a complement:

- The + symbols are replaced with  $\cdot$  symbols and  $\cdot$  symbols with + symbols.

- 2 Each of the terms in the expression is complemented.

The use of De Morgan's theorem may be demonstrated by finding the complement of the expression X + YZ. First, note that a multiplication sign has been omitted and the expression could be written  $X + (Y \cdot Z)$ . To complement this, the addition symbol is replaced with a multiplication symbol and the two terms are complemented, giving  $\overline{X}$  ·  $(\overline{Y}\cdot\overline{Z})$ ; then the remaining term is complemented,  $\overline{X}(\overline{Y} + \overline{Z})$ . The following equivalence has been found:  $(\overline{X} + \overline{Y}\overline{Z}) = \overline{X}(\overline{Y} + \overline{Z})$ .

The complement of  $\overline{W}X + Y\overline{Z}$  may be formed by two steps:

- 1 The addition symbol is changed.

- The complement of each term is formed: 2

$$(\overline{\overline{W} \cdot X})(\overline{Y \cdot \overline{Z}})$$

This becomes  $(W + \overline{X})(\overline{Y} + Z)$ .

Since  $W ext{ and } Z$  were already complemented, they become uncomplemented by the theorem  $\overline{X} = X$ .

It is sometimes necessary to complement both sides of an equation. This may be done in the same way as before:

$$WX + YZ = 0$$

Complementing both sides gives

$$(\overline{WX} + \underline{YZ}) = \overline{0}$$

$$(\overline{W} + \overline{X})(\overline{Y} + \overline{Z}) = 1$$

# **BASIC DUALITY OF BOOLEAN ALGEBRA**

3.11 De Morgan's theorem expresses a basic duality which underlies all boolean algebra. The postulates and theorems which have been presented can all be divided into pairs. For example, (X + Y) + Z = X + (Y + Z) is the dual of (XY)Z =X(YZ), and X + 0 = X is the dual of  $X \cdot 1 = X$ .

Often the rules or theorems are listed in an order which illustrates the duality of the algebra. In proving the theorems or rules of the algebra, it is then necessary to prove only one theorem, and the dual of the theorem follows necessarily. For instance, if you prove that X + XY = X, you can immediately add the theorem X(X + Y) = X to the list of theorems as the dual of the first expression.<sup>8</sup> In effect, all boolean algebra is predicated on this two-for-one basis.

<sup>&</sup>lt;sup>8</sup>When the first expression, X + XY = X, has been complemented,  $\overline{X}(\overline{X} + \overline{Y}) = \overline{X}$  is obtained. Then uncomplemented variables may be substituted on both sides of the equation without changing the basic equivalence of the expression.

DERIVATION OF A BOOLEAN EXPRESSION

# **DERIVATION OF A BOOLEAN EXPRESSION**

**3.12** When designing a logical circuit, the logical designer works from two sets of known values: (1) the various states which the inputs to the logical network can take and (2) the desired outputs for each input condition. The logical expression is derived from these sets of values.

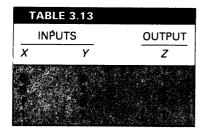

Consider a specific problem. A logical network has two inputs X and Y and an output Z. The relationship between inputs and outputs is to be as follows:

- **1** When both X and Y are 0s, the output Z is to be 1.

- When X is 0 and Y is 1, the output Z is to be 0.

- When X is 1 and Y is 0, the output Z is to be 1.

- 4 When X is 1 and Y is 1, the output Z is to be 1.

These relations may be expressed in tabular form, as shown in Table 3.13.

It is now necessary to add another column to the table. This column will consist of a list of *product terms* obtained from the values of the input variables. The new column will contain each of the input variables listed in each row of the table, with the letter representing the respective input complemented when the input value for this variable is 0 and not complemented when the input value is 1. The terms obtained in this manner are designated as product terms. With two input variables X and Y, each row of the table will contain a product term consisting of X and Y, with X or Y complemented or not, depending on the input values for that row (see Table 3.14).

Whenever Z is equal to 1, the X and Y product term from the same row is removed and formed into a *sum-of-products* expression. Therefore, the product terms from the first, third, and fourth rows are selected. These are  $\overline{XY}$ ,  $\overline{XY}$ , and  $\overline{XY}$ .

| INP | UTS                                   | OUTPUT | PRODUCT |

|-----|---------------------------------------|--------|---------|

| X   | Y                                     | Z      | TERMS   |

| ^   | · · · · · · · · · · · · · · · · · · · | 2      | IEKMS   |

|     | 0                                     | 1      | WP.     |

| •   |                                       | A      | 7       |

BOOLEAN ALGEBRA AND GATE NETWORKS

There are now three terms, each the product of two variables. The logical sum of these products is equal to the expression desired. This type of expression is often referred to as a *canonical expansion* for the function. The complete expression in normal form is

$$\overline{X}\overline{Y} + X\overline{Y} + XY = Z$$

The left-hand side of the expression may be simplified as follows:

$$\overline{X}\overline{Y} + X\overline{Y} + XY = Z

\overline{X}\overline{Y} + X(\overline{Y} + Y) = Z

\overline{X}\overline{Y} + X = Z$$

and finally, by rule 18 in Table 3.10,  $X + \overline{Y} = Z$ .

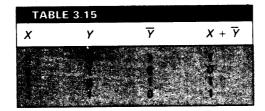

The truth table may be constructed to check the function that has been derived (see Table 3.15). The last column of this table agrees with the last column of the truth table of the desired function, showing that the expressions are equivalent.

The expression  $X + \overline{Y}$  may be constructed in one of two ways. If only the inputs X and Y are available, as might be the case if the inputs to the circuit were from another logical network or from certain types of storage devices, an inverter would be required to form  $\overline{Y}$ . Then the circuit would require an inverter plus an OR gate. Generally the complement of the Y input would be available, however, and only one OR gate would be required for the second way the expression would be constructed.

Another expression, with three inputs (designated X, Y, and Z), will be derived. Assume that the desired relationships between the inputs and the output have been determined, as shown in Table 3.16.

| TABLE 3.16                 |                  |

|----------------------------|------------------|

| INPUTS                     | OUTPUT           |

| Bitten $Y = 0$ , $Y = 0$ . | 2 = 6/3800 Files |

| 0 0                        | Land Browns      |

| 0 1                        | 1 1 4 4 -        |

| i i                        | <b>i</b> . T     |

|                            | 1 5 7            |

|                            |                  |

| TAB         | LE 3.17 |     |              |

|-------------|---------|-----|--------------|

|             | INPUTS  |     | OUTPUT       |

| X           | Y       | Z   |              |

| 0 ,         | 0       | 0   | A farcial as |

| 0           | . 0     | . 1 | 0            |

| 0           | 4       | 1   | o o          |

| 1           | 0       | 0   |              |

| 1           |         | Ó   | ¥ ·          |

| 1 , , , , , | 1       | 1   | 0            |

- 1 A truth table is formed (see Table 3.17).

- **2** A column is added listing the inputs, X, Y, and Z according to their values in the input columns (see Table 3.18).

- The product terms from each row in which the output is a 1 are collected  $(\overline{XYZ}, \overline{XYZ}, \overline{XYZ}, \overline{XYZ}, \text{ and } \overline{XYZ})$ , and the desired expression is the sum of these products  $(\overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XYZ})$ . Therefore, the complete expression in standard form for the desired network is

$$\overline{X}\overline{Y}\overline{Z} + \overline{X}Y\overline{Z} + \dot{X}\overline{Y}\overline{Z} + XY\overline{Z} = A$$

This expression may be simplified as shown below:

Thus the function can be performed by a single inverter connected to the Z input. Inspection of the truth table will indicate that the output A is always equal to the complement of the input variable Z.

| INPUTS |     |   | OUTPUT | PRODUCT |              |

|--------|-----|---|--------|---------|--------------|

| X      | Y   | • | Z      | A       | TERMS        |

|        | 0   |   | 0      |         | XYZ          |

|        | . 0 |   | 1      | 0       | XYZ          |

|        |     |   |        |         |              |

|        |     |   | , i    | ó       | Ž <b>i</b> Ž |

|        | 0   |   | 0      | Ó       |              |

# **INTERCONNECTING GATES**

BOOLEAN ALGEBRA AND GATE NETWORKS

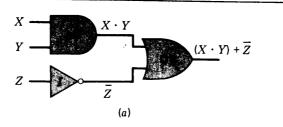

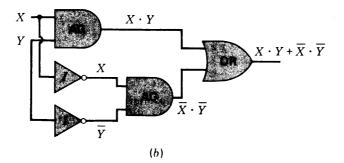

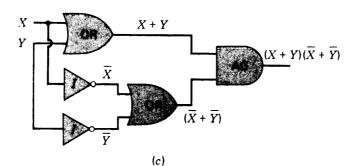

**3.13** The OR gates, AND gates, and inverters described in Secs. 3.3 and 3.4 can be interconnected to form *gating*, or *logic*, *networks*. (Those who study switching theory would also call these *combinational networks*.) The boolean algebra expression corresponding to a given gating network can be derived by systematically progressing from input to output on the gates. Figure 3.5(a) shows a gating network with three inputs X, Y, and Z and an output expression  $(X \cdot Y) + \overline{Z}$ . A network that forms  $(X \cdot Y) + (\overline{X} \cdot \overline{Y})$  and another network that forms  $(X + Y) \cdot (\overline{X} + \overline{Y})$  are shown in Fig. 3.5(b) and (c).

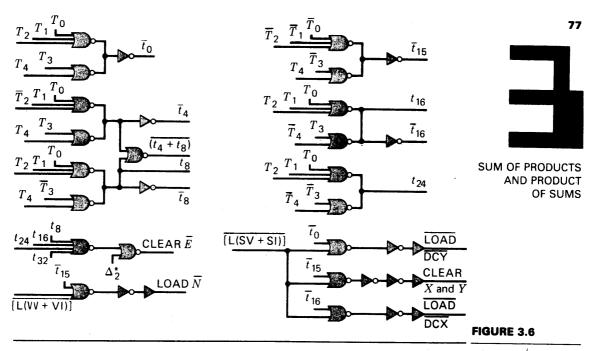

We can analyze the operation of these gating networks by using the boolean algebra expressions. For instance, in troubleshooting a computer, we can determine which gates have failed by examining the inputs to the gating network and the outputs and seeing whether the boolean operations are properly performed. The bookkeeping for computer circuitry is done by means of block diagrams, as in Fig.

# FIGURE 3.5

Three gating networks.

Block diagram from a computer.

3.6, which shows a typical print. The use of boolean algebra is spread completely throughout the computer industry.

# **SUM OF PRODUCTS AND PRODUCT OF SUMS**

**3.14** An important consideration in dealing with gating circuits and their algebraic counterparts is the *form* of the boolean algebra expression and the resulting form of the gating network. Certain types of boolean algebra expressions lead to gating networks which are more desirable from most implementation viewpoints. We now define the two most used and usable forms for boolean expressions.

First let us define terms:

- **1** Product term A product term is a single variable or the logical product of several variables. The variables may or may not be complemented.

- **2** Sum term A sum term is a single variable or the sum of several variables. The variables may or may not be complemented.

For example, the term  $X \cdot Y \cdot Z$  is a product term; X + Y is a sum term; X is both a product term and a sum term;  $X + Y \cdot Z$  is neither a product term nor a sum term;  $X + \overline{Y}$  is a sum term;  $X \cdot \overline{Y} \cdot \overline{Z}$  is a product term;  $\overline{Y}$  is a both a sum term and a product term. (Comment: Calling single variables sum terms and product terms is disagreeable but necessary. Since we must suffer with it, remember that some apples are red, round, and shiny, that is, more than one thing.)

BOOLEAN ALGEBRA AND GATE NETWORKS

We now define two most important types of expressions.

- **1** Sum-of-products expression A sum-of-products expression is a product term or several product terms logically added.

- **2** Product-of-sums expression A product-of-sums expression is a sum term or several sum terms logically multiplied.

For example, the expression  $\overline{X} \cdot Y + X \cdot \overline{Y}$  is a sum-of-products expression;  $(X + Y)(\overline{X} + \overline{Y})$  is a product-of-sums expression. The following are all sum-of-products expressions:

$$X \\ \underline{X} \cdot \underline{Y} + \underline{Z} \\ \overline{X} \cdot \overline{Y} + \overline{X} \cdot \overline{Y} \cdot \overline{Z} \\ X + \underline{Y}$$

The following are product-of-sums expressions:

$$(X + Y) \cdot (X + \overline{Y}) \cdot (\overline{X} + \overline{Y}) (X + Y + Z) \cdot (X + \overline{Y}) \cdot (\overline{X} + \overline{Y}) X + Z \overline{X} (X + Y)X$$

One prime reason for liking sum-of-products or product-of-sums expressions is their straightforward conversion to very nice gating networks. In their purest, nicest form they go into two-level networks, which are networks for which the longest path through which a signal must pass from input to output is two gates.

*Note:* In the following discussion we assume that when a variable X is available, its complement  $\overline{X}$  is also available; that is, no inverters are required to complement inputs. This is quite important and quite realistic, since most signals come from flip-flops, which we study later, and which provide both an output and its complement.

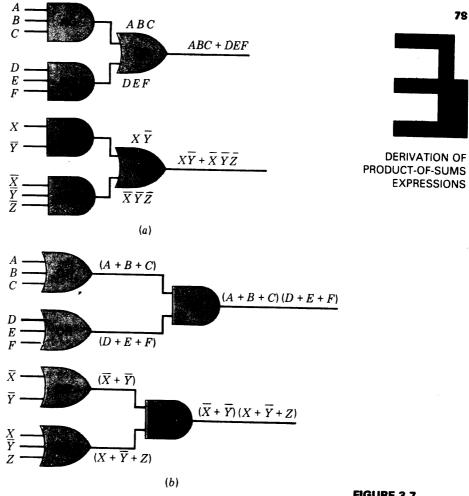

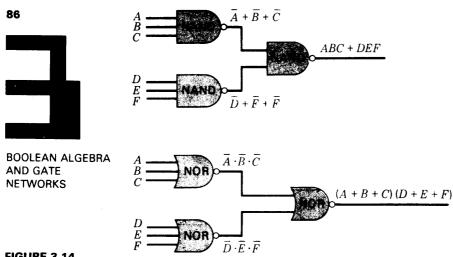

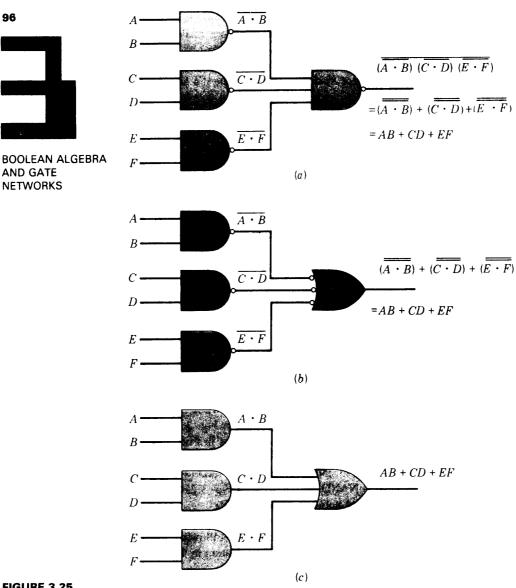

Figure 3.7 shows several gating networks. Figure 3.7(a) shows sum-of-products networks, and Fig. 3.7(b) shows product-of-sums networks. The gating networks for sum-of-products expressions in "conventional" form—that is, expressions with at least two product terms and with at least two variables in each product term—go directly into an AND-to-OR gate network, while conventional product-of-sums expressions go directly into OR-to-AND gate networks, as shown in the figure.

# **DERIVATION OF PRODUCT-OF-SUMS EXPRESSIONS**

**3.15** The sequence of steps described in Sec. 3.12 derived a sum-of-products expression for a given circuit. Another technique, really a dual of the first, forms the required expression as a product-of-sums. The expression derived in this manner is made up, before simplification, of terms each consisting of sums of variables

FIGURE 3.7

(a) AND-to-OR gate networks. (b) OR-to-AND gate networks.

such as (X + Y + Z) .... The final expression is the product of these sum terms and has the form  $(X + Y + Z)(X + Y + \overline{Z}) \cdots (\overline{X} + \overline{Y} + \overline{Z})$ .

The method for arriving at the desired expression is as follows:

- 1 Construct a table of the input and output values.

- 2 Construct an additional column of sum terms containing complemented and uncomplemented variables (depending on the values in the input columns) for each row of the table. In each row of the table, a sum term is formed. However, in this case, if the input value for a given variable is 1, the variable will be complemented; and if 0, no complemented.

- 3 The desired expression is the product of the sum terms from the rows in which the output is 0.

BOOLEAN ALGEBRA AND GATE NETWORKS

| TAB | LE 3.19 | :      |

|-----|---------|--------|

| IN  | PUTS    | OUTPUT |

| X   | Y       | Z      |

| 0   | 0       | 1      |

| 0   | 1       | 0      |

| 1   | 0       | . 0    |

| 1   | 1       | 1 *    |

The use of these rules is illustrated by working examples in this and the following sections.

Table 3.19 contains the input and output values which describe a function to be realized by a logical network.

A column containing the input variables in sum-term form is now added in each row. A given variable is complemented if the input value for the variable is 1 in the same row and is not complemented if the value is 0 (see Table 3.20). Each sum term is, therefore, simply the complement of the product term which occurs in the same row in the previous table for sum-of-products expressions. Notice that the sum term  $\overline{X} + Y$  in the third row of Table 3.20 is the complement of the product term  $X\overline{Y}$  used in the sum-of-products derivation.

A product-of-sums expression is now formed by selecting those sum terms for which the output is 0 and multiplying them. In this case, 0s appear in the second and third rows, showing that the desired expression is  $(X + \overline{Y})(\overline{X} + Y)$ . A sum-of-products expression may be found by multiplying the two terms of this expression, yielding  $XY + \overline{X}\overline{Y}$ . In this case the same number of gates would be required to construct circuits corresponding to both the sum-of-products and the product-of-sums expressions.

# **DERIVATION OF A THREE-INPUT-VARIABLE EXPRESSION**

**3.16** Consider Table 3.21, expressing an input-to-output relationship for which an expression is to be derived. Two columns will be added this time, one containing the sum-of-products terms and the other the product-of-sums terms (see Table 3.22). The two expressions may be written in the following way:

Sum-of-products:

$$\overline{X}Y\overline{Z} + \overline{X}YZ + XY\overline{Z} = A$$

| TABI    | LE 3.20          |               |          |

|---------|------------------|---------------|----------|

| INP     | UTS              | OUTPUT        | SUM      |

| X       | Y                | Z             | TERMS    |

| λ.      |                  |               | X + Y    |

| 0.00    | 18 <b>1</b> 80 m | re and street | 1.0 EA 7 |

| 1       | 0                | 9             | 1.1      |

| A Paris | 1                | <b>1</b>      | X + Y    |

| INPUTS |   |   | OUTPU |  |

|--------|---|---|-------|--|

| X      | Y | Z | A     |  |

| 0      | 0 | 0 | 0     |  |

| 0.     | 0 | 1 | . 0   |  |

| Õ      | 1 | Ĭ | •     |  |

| 1      | 0 | 0 | 0     |  |

| i      | 1 | Ŏ | 1     |  |

| 1      |   | • | 0     |  |

Product-of-sums:

$$(X + Y + Z)(X + Y + \overline{Z})(\overline{X} + Y + Z)(\overline{X} + Y + \overline{Z})(\overline{X} + \overline{Y} + \overline{Z}) = A$$

The two expressions may be simplified as shown:

SUM OF PRODUCTS

$$(\overline{X}Y\overline{Z}) + (\overline{X}YZ) + (XY\overline{Z}) = A$$

$$\overline{X}(Y\overline{Z} + YZ) + (XY\overline{Z}) = A$$

$$\overline{X}Y + XY\overline{Z} = A$$

$$Y(\overline{X} + X\overline{Z}) = A$$

$$\overline{X}Y + Y\overline{Z} = A$$

PRODUCT OF SUMS

$$(X+Y+Z)(X+Y+\overline{Z})(\overline{X}+Y+Z)(\overline{X}+Y+\overline{Z})(\overline{X}+\overline{Y}+\overline{Z}) = A \\ (X+Y)(\overline{X}+Y)(\overline{X}+\overline{Z}) = A \\ Y(\overline{X}+\overline{Z}) = A$$

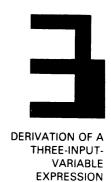

The two final expressions clearly can be seen to be equivalent. Notice, however, that the shortest sum-of-products expression, which is  $\overline{X}Y + Y\overline{Z}$ , requires two AND gates and an OR gate (Fig. 3.8), while the shortest product-of-sums expression,  $Y(\overline{X} + \overline{Z})$ , requires only a single AND gate and a single OR gate. In some cases the minimal sum-of-products expression will require fewer logical elements to construct, and in other instances the construction of the minimal product

| INPUTS |     |     | OUTPUT | PRODUCT      |                |

|--------|-----|-----|--------|--------------|----------------|

| X      | Y   | Z   | A      | TERMS        | SUM TERMS      |

|        | . 0 | . 0 | 0      | XYZ          | *******        |

|        |     | 0   |        | X /2         | X+¥+3<br>X+V+3 |

|        | 1   | 1   | 1      | χ <u>γ</u> χ | 4+2+2          |

|        | ā   | 100 | 6      | . Crim       | ※ 基工を1分        |

#### FIGURE 3.8

Networks for  $Y(\overline{X} + \overline{Z})$  and  $\overline{X}Y + Y\overline{Z}$ .

of sums will require fewer elements. If the sole criterion is the number of logical elements, it is necessary to obtain both a minimal sum-of-products expression and a minimal product-of-sums expression to compare the two. It is possible first to derive the canonical expansion expression for the network to be designed in one of the forms—for instance, product of sums—to simplify the expression, and then to convert the simplified expression to the other form, by using the distributive laws. Then any additional simplification which is required can be performed. In this way, minimal expressions in each form may be obtained without deriving both canonical expansions, although this may be desirable.

The simplification techniques which have been described are algebraic and depend on judicious use of the theorems that have been presented. The problem of simplifying boolean expressions so that the shortest expression is always found is quite complex. However, it is possible, by means of the repeated use of certain algorithms, to derive minimal sum-of-products and product-of-sums expressions. We examine this problem in following sections.

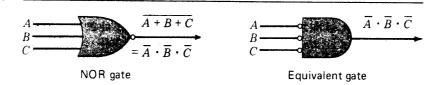

# **NAND GATES AND NOR GATES**